TOSHIBA

## TX System RISC TX79 Core Architecture

## (Symmetric 2-way superscalar 64-bit CPU) Rev. 2.0

**TOSHIBA CORPORATION**

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The Toshiba products listed in this document are intended for usage in general electronics applications ( computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba products listed in this document shall be made at the customer's own risk.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

#### Preface

Thank you for choosing Toshiba semiconductor products. This is the year 2000 edition of the user's manual for the architecture of the TX79 RISC microprocessor core, a member of the TX System RISC Family of Toshiba microprocessors.

This user's manual is designed to be easily understood by engineers who are designing a Toshiba microprocessor into their products for the first time. No special knowledge of this architecture is assumed – the contents includes basic information about the architecture of the TX79 microprocessor core as well as more advanced, in-depth description.

Toshiba are continually updating technical publications. Any comments and suggestions regarding any Toshiba document are most welcome and will be taken into account when subsequent editions are prepared. To receive updates to the information in this manual, or for additional information about this architecture, please contact your nearest Toshiba office or authorized Toshiba dealer.

April 2001

## **CONTENTS**

### Handling Precautions

### C790 User's Manual

| 1. | Intro | odu    | ction                                                                       | 1-1  |

|----|-------|--------|-----------------------------------------------------------------------------|------|

| 1  | .1    | Fea    | tures                                                                       | 1-2  |

| 1  | .2    | Rela   | ated Documents                                                              | 1-3  |

| 1  | .3    | Rev    | ision History                                                               | 1-4  |

| 1  | .4    | Con    | ventions Used in This Manual                                                | 1-5  |

| 1  | .5    | Res    | trictions for Use of the C790 CPU Core                                      | 1-6  |

| 2. | Arc   | hite   | cture Overview                                                              | 2-1  |

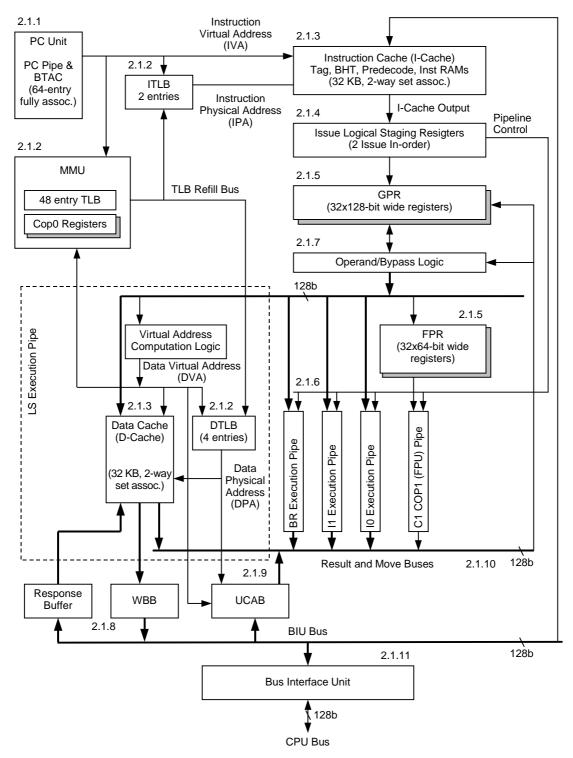

| 2  | .1    | Bloc   | k Diagram and Functional Block Descriptions                                 | 2-2  |

|    | 2.1.  | 1      | PC Unit                                                                     | 2-3  |

|    | 2.1.  | 2      | MMU                                                                         | 2-3  |

|    | 2.1.  | 3      | Caches                                                                      | 2-3  |

|    | 2.1.  | 4      | Issue Logic and Staging Registers                                           | 2-3  |

|    | 2.1.  | 5      | GPR (General Purpose Registers) and FPR (Floating-Point Registers)          | 2-3  |

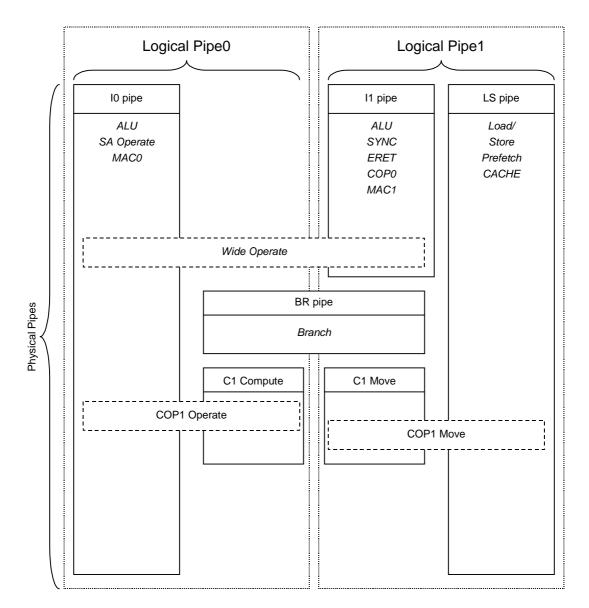

|    | 2.1.  | 6      | The Five Execution Pipes                                                    | 2-3  |

|    | 2.    | .1.6.  | 1 I0 and I1 Pipes                                                           | 2-3  |

|    | 2.    | .1.6.  | 2 LS - Load/Store Pipe                                                      | 2-3  |

|    | 2.    | .1.6.3 | 3 BR - Branch Pipe                                                          | 2-3  |

|    | 2.    | .1.6.  | 4 C1 - COP1/FPU Pipe                                                        | 2-3  |

|    | 2.1.  |        | Operand/Bypass logic                                                        |      |

|    | 2.1.  |        | Response Buffer and Writeback Buffer                                        |      |

|    | 2.1.  | 9      | UCAB                                                                        | 2-4  |

|    | 2.1.  | -      | Result and Move Buses                                                       |      |

|    | 2.1.  | 11     | Bus Interface Unit and BIU Bus                                              | 2-4  |

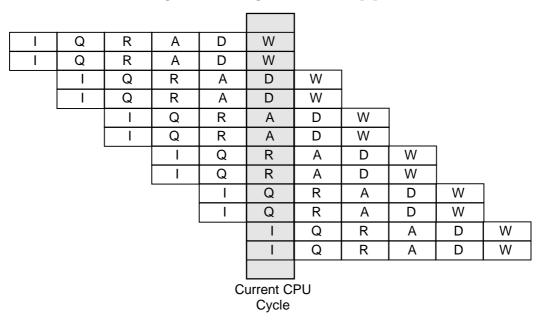

| 2  | .2    | Sup    | erscalar Pipeline Operation                                                 | 2-5  |

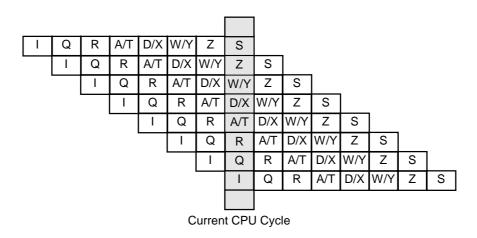

|    | 2.2.  | 1      | Integer Instruction Pipeline Stages                                         | 2-5  |

|    | 2.2.  | 2      | C1 (COP1/FPU) Instruction Pipeline Stages                                   | 2-8  |

|    | 2.2.  | 3      | Classification and Routing of Instructions According to Execution Pipelines | 2-10 |

|    | 2.2.  | 4      | Instruction Issue Combinations                                              | 2-12 |

| 2  | .3    | Reg    | isters                                                                      | 2-14 |

|    | 2.3.  | 1      | CPU Registers                                                               | 2-14 |

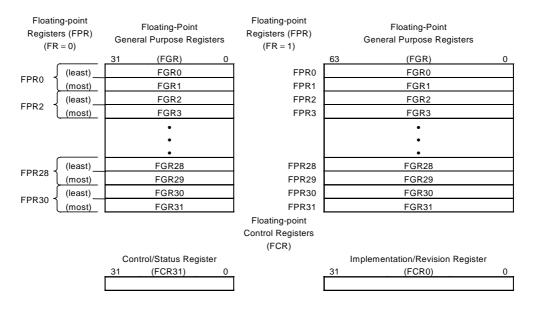

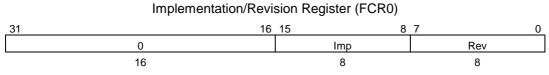

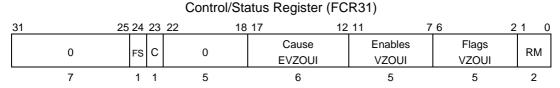

|    | 2.3.  | 2      | FPU Registers                                                               | 2-14 |

|    | 2.3.  | 3      | COP0 Registers                                                              | 2-15 |

i

| 2.5       Cache Memory       2         2.6       Bus Interface       2         2.7       Floating Point Unit       2         2.8       Performance Counter       2         2.9       Debug and Tracing Functions       2         3.       Instruction Set Overview and Summary       2         3.1       Introduction       2         3.2       CPU Instruction Set Formats       3         3.3       Instruction Set Summary       3.3.1         3.3.1.1       Normal Loads and Stores       3.3.1.2 | 2-18<br>2-19<br>2-19<br>2-19<br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5<br>.3-5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <ul> <li>2.7 Floating Point Unit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-18<br>2-19<br>2-19<br>.3-1<br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5<br>.3-5 |

| <ul> <li>2.8 Performance Counter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-19<br>2-19<br>. <b>3-1</b><br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5<br>.3-5 |

| <ul> <li>2.9 Debug and Tracing Functions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-19<br>. <b>3-1</b><br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                 |

| <ul> <li>3. Instruction Set Overview and Summary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>.3-1</b><br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                          |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                                         |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                                         |

| <ul> <li>3.2 CPU Instruction Set Formats</li> <li>3.3 Instruction Set Summary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                               | .3-3<br>.3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                                                 |

| <ul> <li>3.3 Instruction Set Summary</li> <li>3.3.1 Load/Store Instructions</li> <li>3.3.1.1 Normal Loads and Stores</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       | .3-4<br>.3-4<br>.3-4<br>.3-5<br>.3-5                                                         |

| 3.3.1 Load/Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .3-4<br>.3-4<br>.3-5<br>.3-5                                                                 |

| 3.3.1.1 Normal Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .3-4<br>.3-5<br>.3-5                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .3-5<br>.3-5                                                                                 |

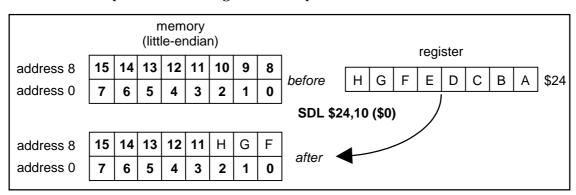

| 3.3.1.2 Multimedia Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .3-5                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 3.3.1.3 Coprocessor Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 5                                                                                          |

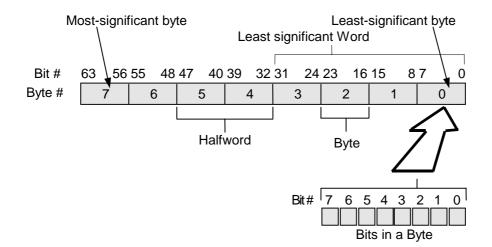

| 3.3.1.4 Data Formats and Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .3-5                                                                                         |

| 3.3.1.5 Defining Access Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 3.3.1.6 Scheduling a Load Delay Slot                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 3.3.2 Computational Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.3.2.1 ALU Immediate Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

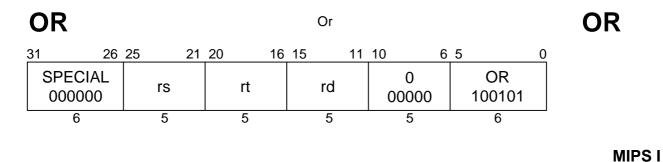

| 3.3.2.2 Three Operand Register-Type Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.3.2.3 Shift Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |

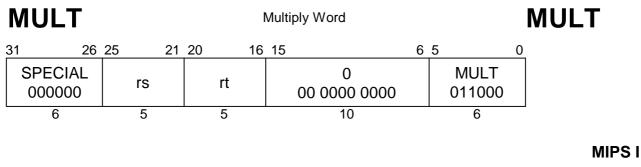

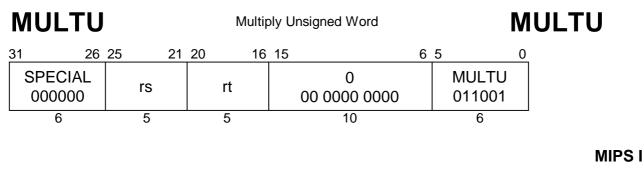

| 3.3.2.4 Multiply and Divide Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 3.3.2.5 64-Bit Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 3.3.3 Jump and Branch Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.3.3.1 Jump Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 3.3.3.2 Branch Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

| 3.3.4 Miscellaneous Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.3.4.1 Exception Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.3.4.2 Serialization Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.3.4.3 MIPS IV Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 3.3.5 System Control Coprocessor (COP0) Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

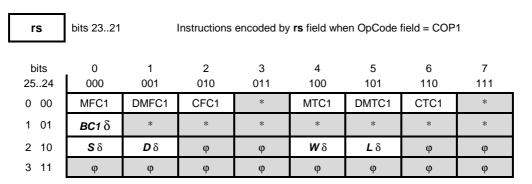

| 3.3.6 Coprocessor 1 (COP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |

| 3.3.6.1 Coprocessor 1 (COP1) Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 3.3.7 C790-Specific Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.3.7.1 Integer Multiply / Divide Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.3.7.2 Multimedia Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 3.4 User Instruction Latency and Repeat Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-25                                                                                         |

| 4. CPU and COP0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .4-1                                                                                         |

| 4.1 CPU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

### TOSHIBA

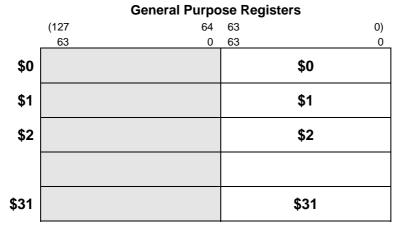

| 4.    | 1.1    | General Purpose Registers                        | 4-4  |

|-------|--------|--------------------------------------------------|------|

| 4.    | 1.2    | HI and LO Registers                              | 4-4  |

| 4.    | 1.3    | Shift Amount (SA) Register                       | 4-4  |

| 4.    | 1.4    | Program Counter (PC)                             | 4-4  |

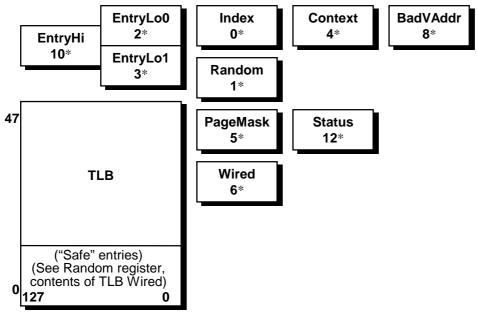

| 4.2   | Sys    | stem Control Coprocessor (COP0) Registers        | 4-5  |

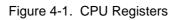

| 4.    | 2.1    | Index Register (0)                               | 4-6  |

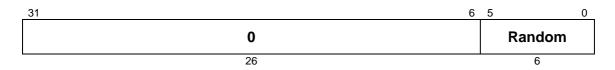

| 4.    | 2.2    | Random Register (1)                              | 4-7  |

| 4.    | 2.3    | EntryLo0 Register (2), and EntryLo1 Register (3) | 4-8  |

| 4.    | 2.4    | Context Register (4)                             | 4-9  |

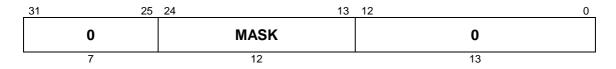

| 4.    | 2.5    | PageMask Register (5)                            | 4-10 |

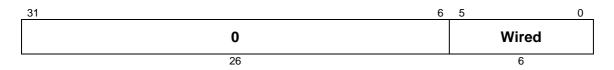

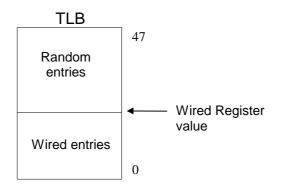

| 4.    | 2.6    | Wired Register (6)                               | 4-11 |

| 4.    | 2.7    | BadVAddr Register (8)                            | 4-12 |

| 4.    | 2.8    | Count Register (9)                               | 4-13 |

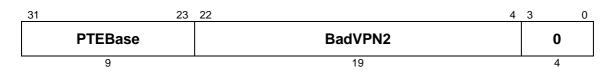

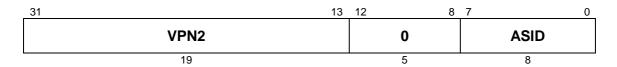

| 4.    | 2.9    | EntryHi Register (10)                            | 4-14 |

| 4.    | 2.10   | Compare Register (11)                            | 4-15 |

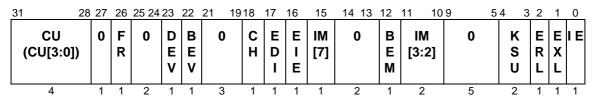

| 4.    | 2.11   | Status Register (12)                             | 4-16 |

|       | 4.2.1  | 1.1 Status Register Format                       | 4-17 |

|       |        | 1.2 Status Register Modes and Access States      |      |

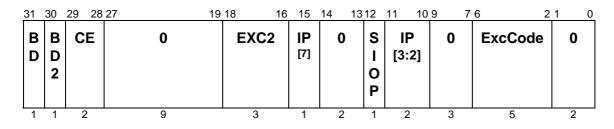

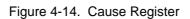

| 4.    | 2.12   | Cause Register (13)                              | 4-19 |

| 4.    | 2.13   | EPC Register (14)                                | 4-21 |

| 4.    | 2.14   | PRId Register (15)                               | 4-22 |

| 4.    | 2.15   | Config Register (16)                             | 4-23 |

| 4.    | 2.16   | BadPAddr Register (23)                           | 4-25 |

| 4.    | 2.17   | Debug Registers (24)                             | 4-26 |

| 4.    | 2.18   | Performance Counter Registers (25)               | 4-28 |

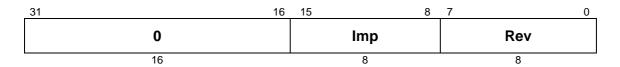

| 4.    | 2.19   | TagLo (28) and TagHi (29) Registers              | 4-31 |

| 4.    | 2.20   | ErrorEPC (30)                                    | 4-33 |

| 5. Ex | xcepti | tion Processing and Reset                        | 5-1  |

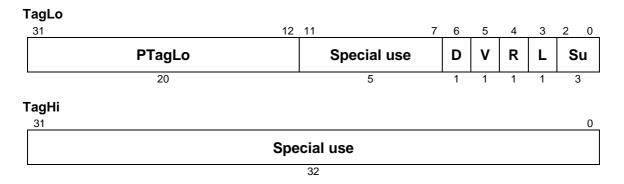

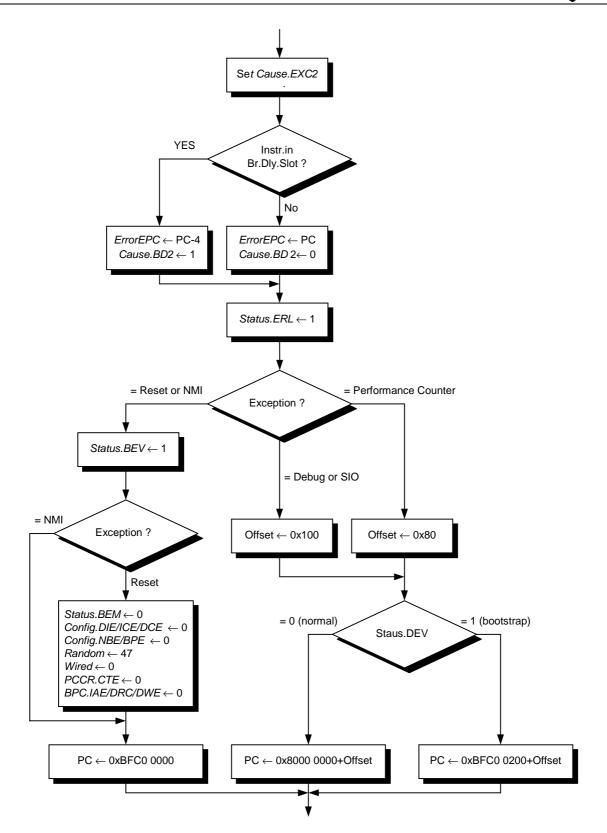

| 5.1   | The    | e Exception Handling Process                     | 5-2  |

| 5.    | 1.1    | Level 1 Exceptions                               | 5-2  |

| 5.    | 1.2    | Level 2 Exceptions                               | 5-5  |

| 5.2   | Exc    | ception Vector Locations                         | 5-7  |

| 5.3   | Cau    | use Register Setting                             | 5-8  |

| 5.4   | Mas    | isking an exception                              | 5-9  |

| 5.5   |        | taild Description                                |      |

| 5.    | 5.1    | Exception Priority                               | 5-10 |

| 5.    | 5.2    | Reset Exception                                  | 5-11 |

| 5.    | 5.3    | Non-Maskable Interrupt (NMI) Exception           | 5-12 |

| 5.    | 5.4    | Performance Counter Exception                    | 5-13 |

| •• |                |                                             |      |

|----|----------------|---------------------------------------------|------|

| 7. | Caches         | 7-1                                         |      |

| 6  |                | ء<br>Instructions                           |      |

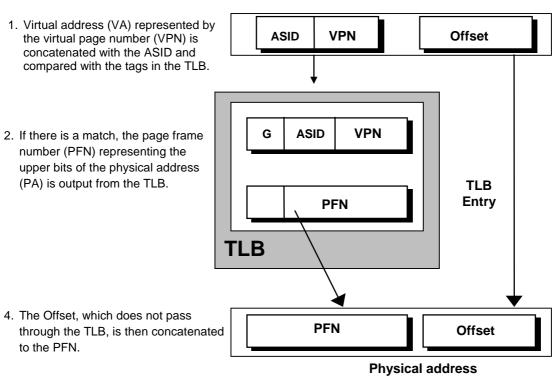

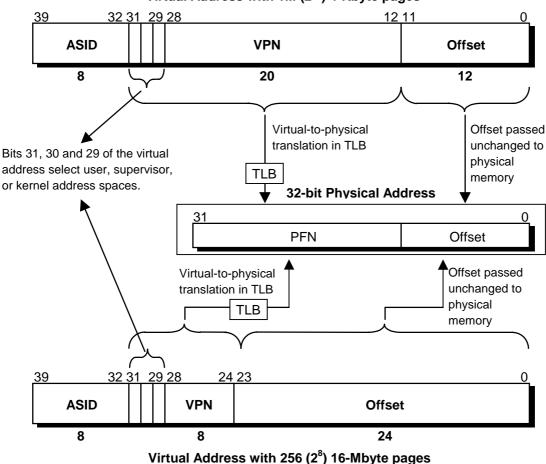

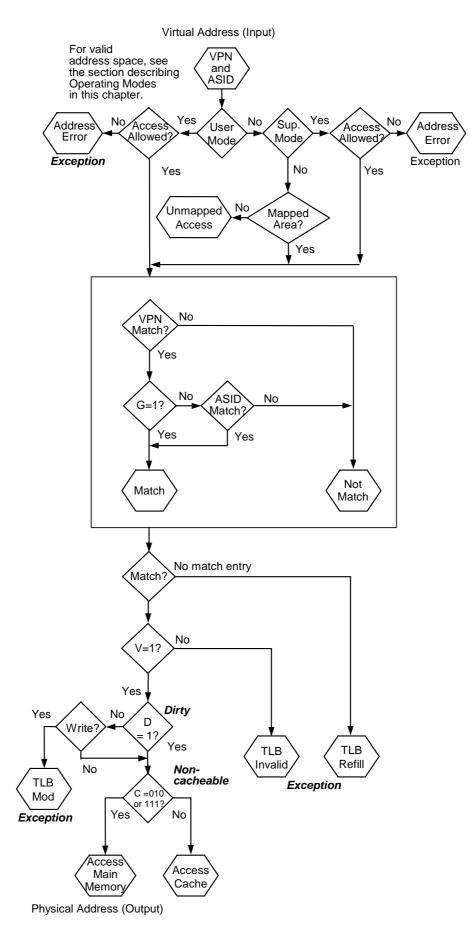

| e  | 6.4 Virt       | ual-to-Physical Address Translation Process |      |

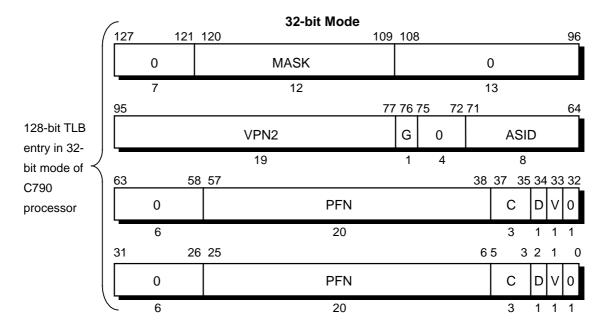

|    | 6.3.1          | Format of a TLB Entry                       |      |

| 6  |                | tem Control Coprocessor                     |      |

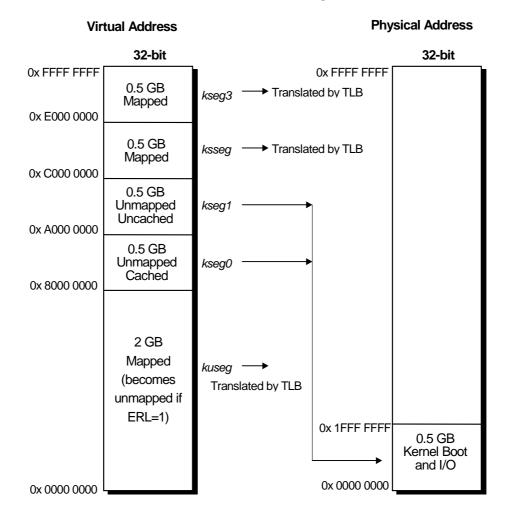

|    | 6.2.8          | Kernel Mode Operations                      |      |

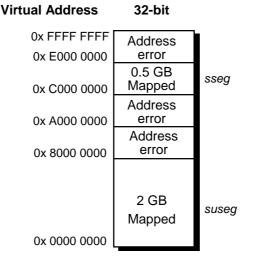

|    | 6.2.7          | Supervisor Mode Operations                  |      |

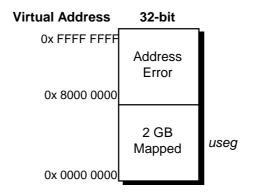

|    | 6.2.6          | User Mode Operations                        |      |

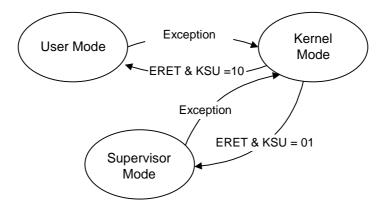

|    | 6.2.4          | Operating Modes                             |      |

|    | 6.2.4          | 32-bit Address Translation Mode             |      |

|    | 6.2.2          | Virtual-to-Physical Address Translation     |      |

|    | 6.2.1          | Physical Address Space                      |      |

| C  | 6.2.1          | Virtual Address Space                       |      |

| c  |                | Iress Spaces                                |      |

|    | 6.1.1<br>6.1.2 | Translation Status<br>Multiple Matches      |      |

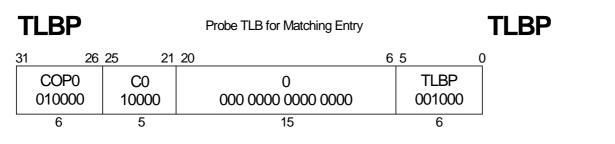

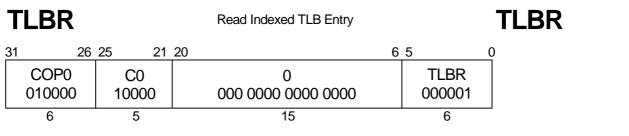

| C  |                | nslation Look-aside Buffer (TLB)            |      |

|    |                | -                                           |      |

| 6. | Memor          | y Management                                | 6-1  |

|    | 5.5.19         | Floating-Point Exception                    | 5-28 |

|    | 5.5.18         | Trap Exception                              | 5-27 |

|    | 5.5.17         | Integer Overflow Exception                  | 5-26 |

|    | 5.5.16         | SIO Exception                               | 5-25 |

|    | 5.5.15         | Interrupt Exception                         | 5-24 |

|    | 5.5.14         | Coprocessor Unusable Exception              | 5-23 |

|    | 5.5.13         | Reserved Instruction Exception              | 5-22 |

|    | 5.5.12         | BREAK Instruction Exception                 | 5-21 |

|    | 5.5.11         | System Call Exception                       | 5-20 |

|    | 5.5.10         | Bus Error Exception                         | 5-19 |

|    | 5.5.9          | TLB Modified Exception                      | 5-18 |

|    | 5.5.8          | TLB Invalid Exception                       | 5-17 |

|    | 5.5.7          | TLB Refill Exception                        | 5-16 |

|    | 5.5.6          | Address Error Exception                     | 5-15 |

|    | 5.5.5          | Debug Exception                             | 5-14 |

| 7.1 | Cad | che Features            | 7-2 |

|-----|-----|-------------------------|-----|

| 7.2 | Org | anization of the Caches | 7-3 |

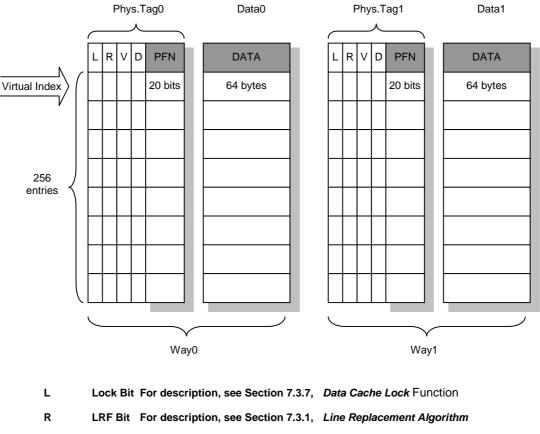

| 7.2 | .1  | Data Cache              | 7-3 |

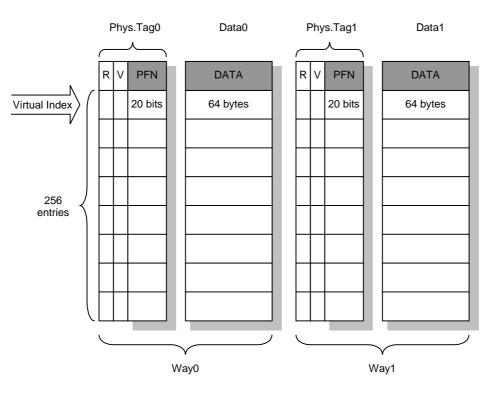

| 7.2 | .2  | Instruction Cache       | 7-4 |

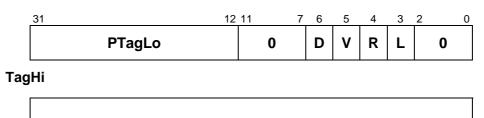

| 7.2 | .3  | Tag Structure           | 7-5 |

|     |     |                         |     |

| 7.2.3                                                                                              | 1 Data Cache Tag Structure                                                                                                                                                                                                                                                                                   | 7-6                                                                                        |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 7.2.3                                                                                              | 2 Instruction Cache Tag Structure                                                                                                                                                                                                                                                                            | 7-6                                                                                        |

| 7.2.4                                                                                              | State of Cache Tags After Reset                                                                                                                                                                                                                                                                              | 7-7                                                                                        |

| 7.3 Ca                                                                                             | he Operations                                                                                                                                                                                                                                                                                                | 7-8                                                                                        |

| 7.3.1                                                                                              | Line Replacement Algorithm                                                                                                                                                                                                                                                                                   | 7-8                                                                                        |

| 7.3.2                                                                                              | Non-blocking Loads and Hit Under Miss                                                                                                                                                                                                                                                                        | 7-8                                                                                        |

| 7.3.3                                                                                              | Cache Miss and Hit Operations                                                                                                                                                                                                                                                                                | 7-9                                                                                        |

| 7.3.4                                                                                              | Data Cache Writeback Policy                                                                                                                                                                                                                                                                                  | 7-10                                                                                       |

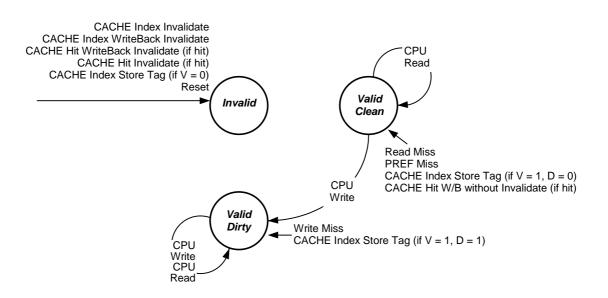

| 7.3.5                                                                                              | Data Cache State Transitions                                                                                                                                                                                                                                                                                 | 7-11                                                                                       |

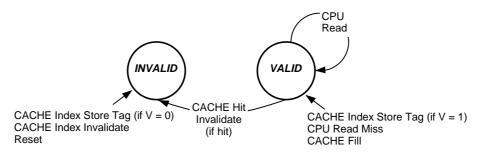

| 7.3.6                                                                                              | Instruction Cache State Transitions                                                                                                                                                                                                                                                                          | 7-12                                                                                       |

| 7.3.7                                                                                              | Data Cache Lock Function                                                                                                                                                                                                                                                                                     | 7-12                                                                                       |

| 7.3.7                                                                                              | 1 Operations During Lock                                                                                                                                                                                                                                                                                     | 7-13                                                                                       |

| 7.3.8                                                                                              | Relationship Between Cached and Uncached Operations                                                                                                                                                                                                                                                          | 7-13                                                                                       |

| 7.4 Un                                                                                             | cached Accelerated Buffer                                                                                                                                                                                                                                                                                    | 7-14                                                                                       |

| 7.4.1                                                                                              | UCAB Configuration                                                                                                                                                                                                                                                                                           | 7-14                                                                                       |

| 7.4.2                                                                                              | Tag Structure                                                                                                                                                                                                                                                                                                | 7-14                                                                                       |

| 7.4.3                                                                                              | Non-blocking Loads and HiT under Miss                                                                                                                                                                                                                                                                        | 7-14                                                                                       |

| 7.5 Ca                                                                                             | he Control Registers                                                                                                                                                                                                                                                                                         | 7-15                                                                                       |

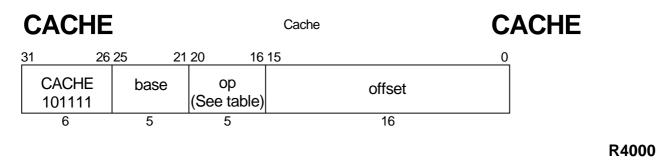

| 7.6 CA                                                                                             | CHE Instruction                                                                                                                                                                                                                                                                                              | 7-16                                                                                       |

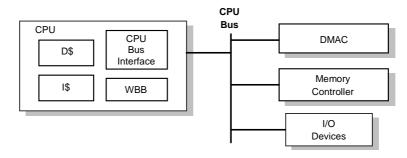

| 8. CPU B                                                                                           | IS                                                                                                                                                                                                                                                                                                           | 0.4                                                                                        |

|                                                                                                    |                                                                                                                                                                                                                                                                                                              |                                                                                            |

|                                                                                                    |                                                                                                                                                                                                                                                                                                              |                                                                                            |

| 8.1.1                                                                                              | Terminology                                                                                                                                                                                                                                                                                                  |                                                                                            |

| 8.1.2                                                                                              | Signal Naming Convention                                                                                                                                                                                                                                                                                     |                                                                                            |

|                                                                                                    | J Bus Architecture                                                                                                                                                                                                                                                                                           |                                                                                            |

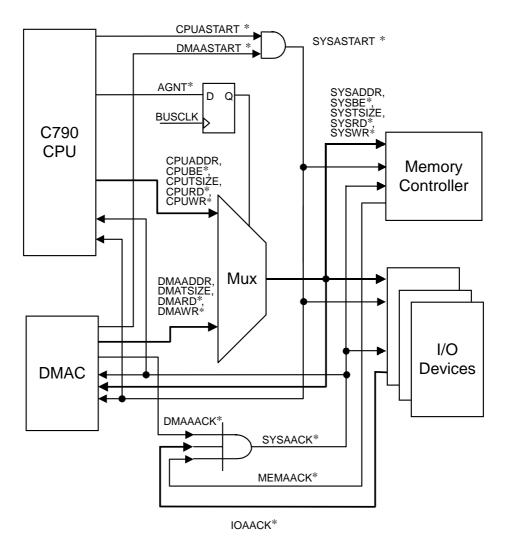

|                                                                                                    | CPU Bus Connectivity for Address and Control Paths                                                                                                                                                                                                                                                           | 8-5                                                                                        |

| 8.2.2                                                                                              |                                                                                                                                                                                                                                                                                                              |                                                                                            |

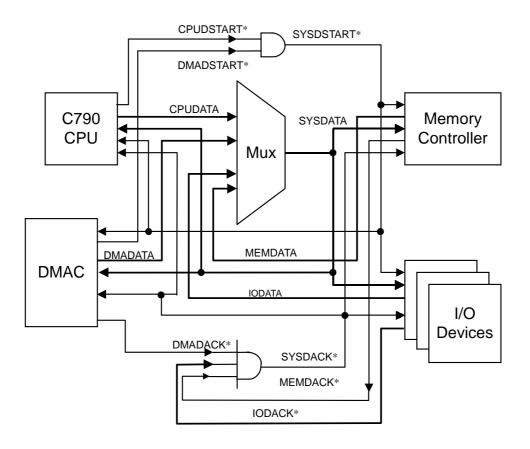

|                                                                                                    | CPU Bus Connectivity for Data Paths                                                                                                                                                                                                                                                                          |                                                                                            |

|                                                                                                    | J Bus Signal Descriptions                                                                                                                                                                                                                                                                                    | 8-7                                                                                        |

| 8.3.1                                                                                              | J Bus Signal Descriptions<br>Address Bus Signals                                                                                                                                                                                                                                                             | 8-7<br>8-7                                                                                 |

| 8.3.1<br>8.4 Ov                                                                                    | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations                                                                                                                                                                                                                             | 8-7<br>8-7<br>8-12                                                                         |

| 8.3.1<br>8.4 Ove<br>8.4.1                                                                          | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations                                                                                                                                                                                                       | 8-7<br>8-7<br>8-12<br>8-12                                                                 |

| 8.3.1<br>8.4 Ov<br>8.4.1<br>8.4.2                                                                  | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests                                                                                                                                                                                 | 8-7<br>8-7<br>8-12<br>8-12<br>8-12                                                         |

| 8.3.1<br>8.4 Ov<br>8.4.1<br>8.4.2<br>8.4.2                                                         | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests                                                                                                                                                              | 8-7<br>8-7<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12                                         |

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2                                               | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests                                                                                                                                          | 8-7<br>8-7<br>8-12<br>8-12<br>8-12<br>8-12<br>8-13                                         |

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2<br>8.4.3                                      | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests<br>Bus Error Operations                                                                                                                  | 8-7<br>8-7<br>8-12<br>8-12<br>8-12<br>8-12<br>8-13<br>8-13                                 |

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2<br>8.4.3<br>8.5 CP                            | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests<br>Bus Error Operations<br>J Bus Transaction Protocols and Timing                                                                        |                                                                                            |

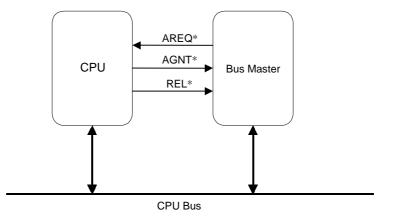

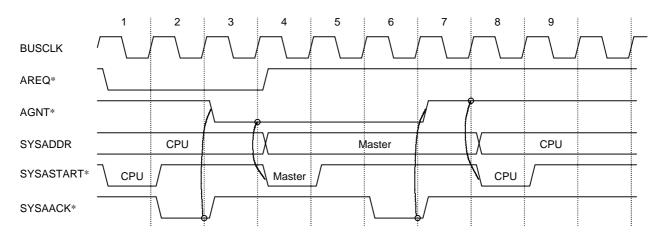

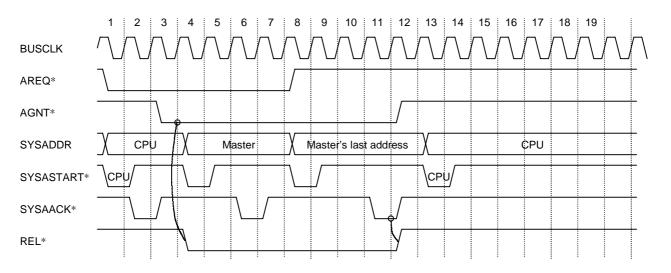

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2<br>8.4.3<br>8.5 CP<br>8.5.1                   | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests<br>Bus Error Operations<br>J Bus Transaction Protocols and Timing<br>Arbitration Operations                                              |                                                                                            |

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2<br>8.4.3<br>8.5 CP<br>8.5.1<br>8.5.1<br>8.5.1 | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests<br>Bus Error Operations<br>J Bus Transaction Protocols and Timing<br>Arbitration Operations<br>1 Cycle Stealing                          | 8-7<br>8-7<br>8-12<br>8-12<br>8-12<br>8-12<br>8-13<br>8-13<br>8-13<br>8-14<br>8-14<br>8-15 |

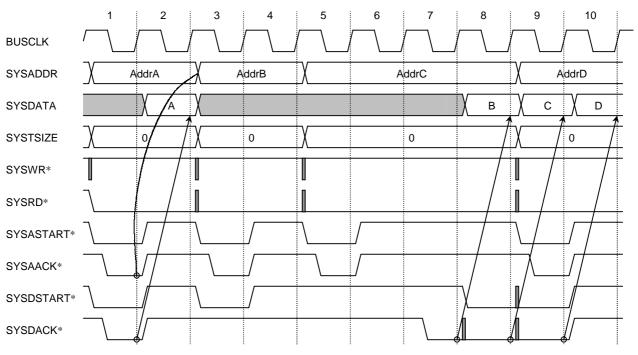

| 8.3.1<br>8.4 Ove<br>8.4.1<br>8.4.2<br>8.4.2<br>8.4.2<br>8.4.3<br>8.5 CP<br>8.5.1                   | J Bus Signal Descriptions<br>Address Bus Signals<br>erview of CPU Bus Operations<br>CPU Bus Operations<br>Processor Requests<br>1 Read Requests<br>2 Write Requests<br>Bus Error Operations<br>J Bus Transaction Protocols and Timing<br>Arbitration Operations<br>1 Cycle Stealing<br>CPU Single Operations |                                                                                            |

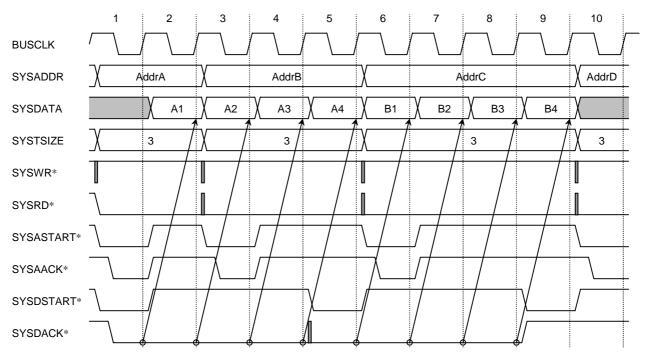

|                                                                                                                                   | 8.5.2.2                                                                                                                                                                                           | CPU Single Writes                                                                                                                                                                                                                                                                     | 8-17                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

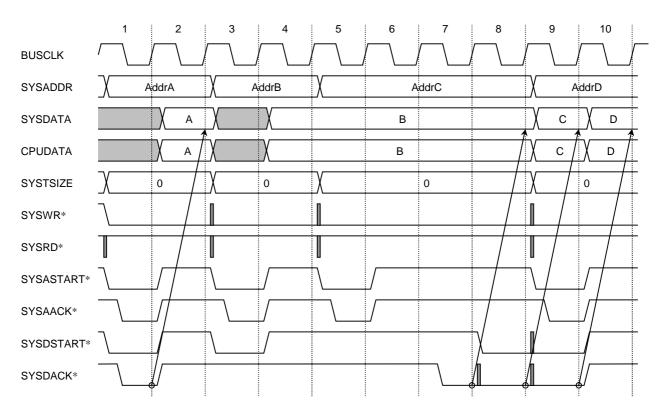

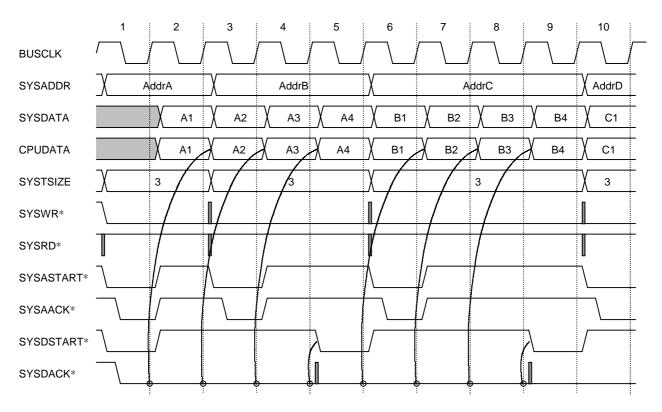

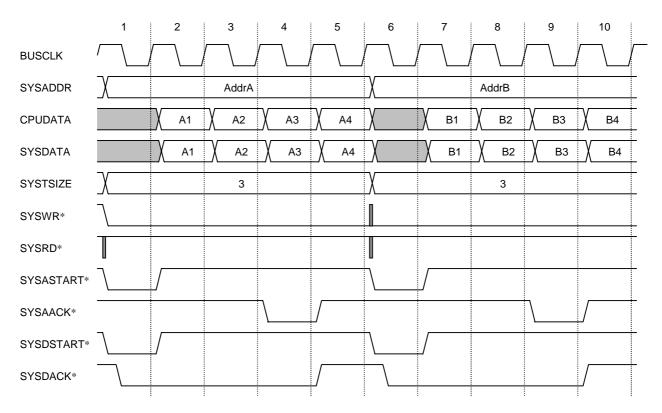

|                                                                                                                                   | 8.5.2.3                                                                                                                                                                                           | CPU Single Read-Write-Read-Write Cycles                                                                                                                                                                                                                                               | 8-18                                                                                                                                  |

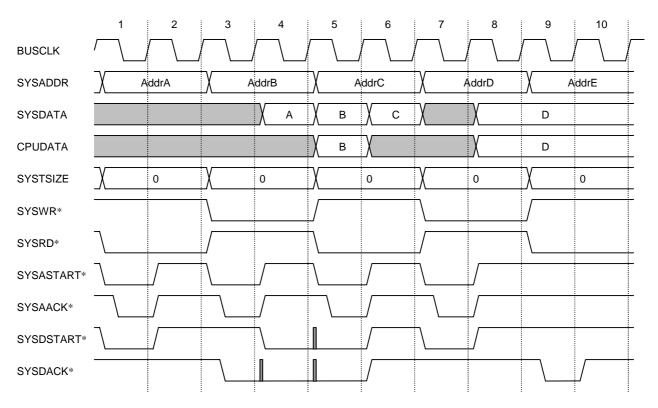

| 8.                                                                                                                                | 5.3 CF                                                                                                                                                                                            | PU Burst Operations                                                                                                                                                                                                                                                                   | 8-19                                                                                                                                  |

|                                                                                                                                   | 8.5.3.1                                                                                                                                                                                           | CPU Burst Reads                                                                                                                                                                                                                                                                       | 8-19                                                                                                                                  |

|                                                                                                                                   | 8.5.3.2                                                                                                                                                                                           | CPU Burst Writes                                                                                                                                                                                                                                                                      | 8-20                                                                                                                                  |

|                                                                                                                                   | 8.5.3.3                                                                                                                                                                                           | CPU Burst Read-Write Cycles                                                                                                                                                                                                                                                           | 8-21                                                                                                                                  |

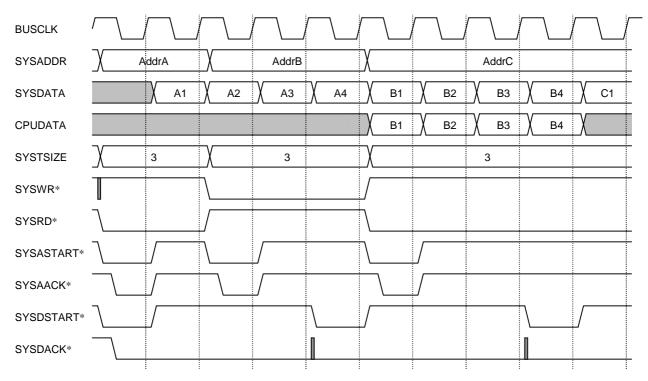

|                                                                                                                                   | 8.5.3.4                                                                                                                                                                                           | CPU Burst Write-Read Cycles                                                                                                                                                                                                                                                           | 8-21                                                                                                                                  |

| 8.                                                                                                                                | 5.4 CF                                                                                                                                                                                            | PU Non-Pipeline Single Operations                                                                                                                                                                                                                                                     | 8-22                                                                                                                                  |

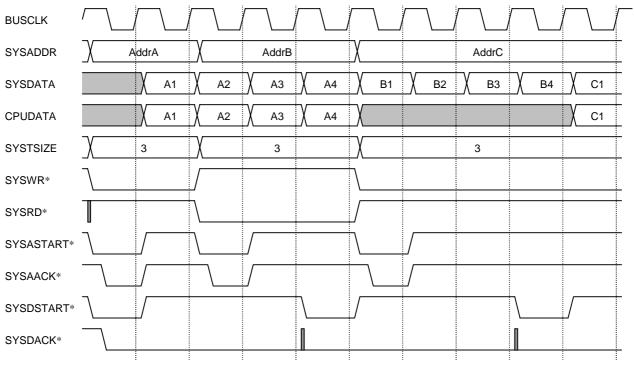

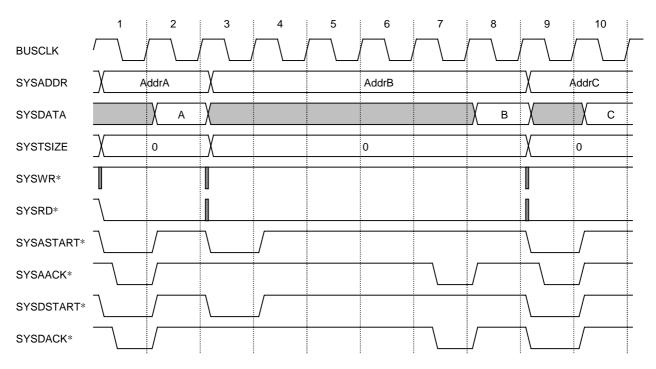

|                                                                                                                                   | 8.5.4.1                                                                                                                                                                                           | CPU Non-Pipeline Single Reads                                                                                                                                                                                                                                                         | 8-22                                                                                                                                  |

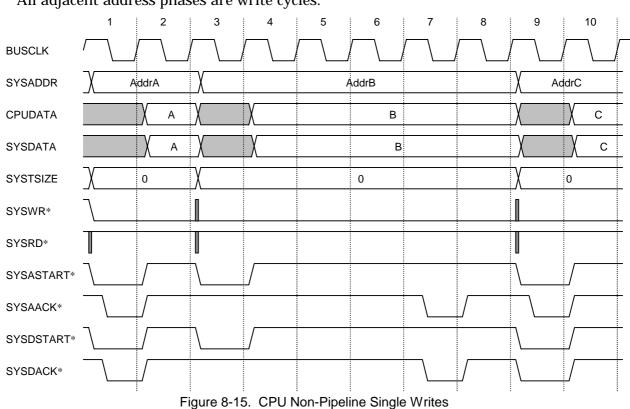

|                                                                                                                                   | 8.5.4.2                                                                                                                                                                                           | CPU Non-Pipeline Single Writes                                                                                                                                                                                                                                                        | 8-23                                                                                                                                  |

| 8.                                                                                                                                | 5.5 CF                                                                                                                                                                                            | PU Non-Pipeline Burst Operations                                                                                                                                                                                                                                                      | 8-23                                                                                                                                  |

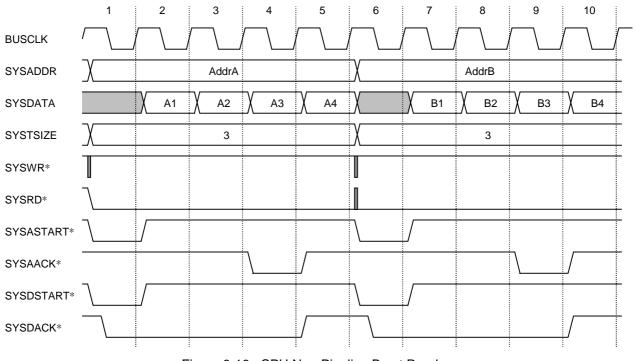

|                                                                                                                                   | 8.5.5.1                                                                                                                                                                                           | CPU Non-Pipeline Burst Reads                                                                                                                                                                                                                                                          | 8-23                                                                                                                                  |

|                                                                                                                                   | 8.5.5.2                                                                                                                                                                                           | CPU Non-Pipeline Burst Writes                                                                                                                                                                                                                                                         | 8-24                                                                                                                                  |

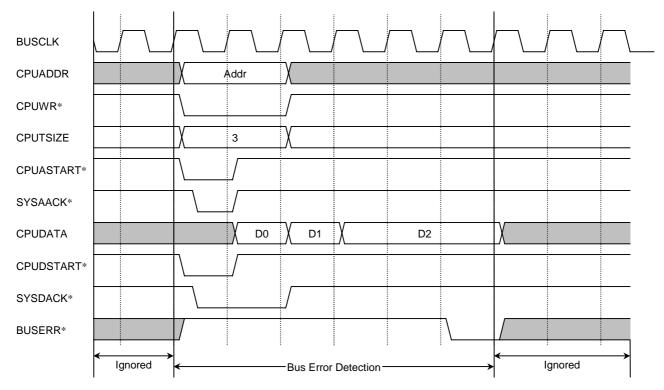

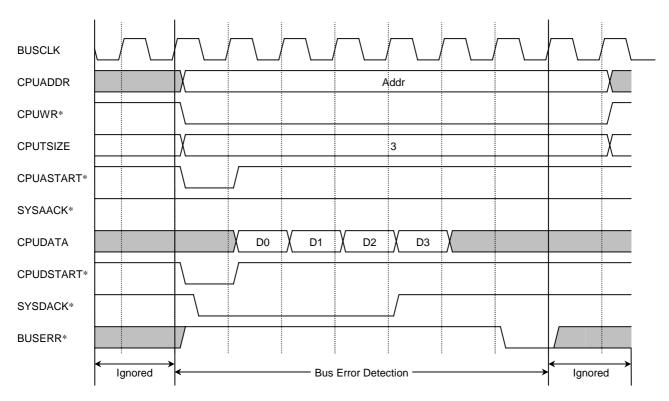

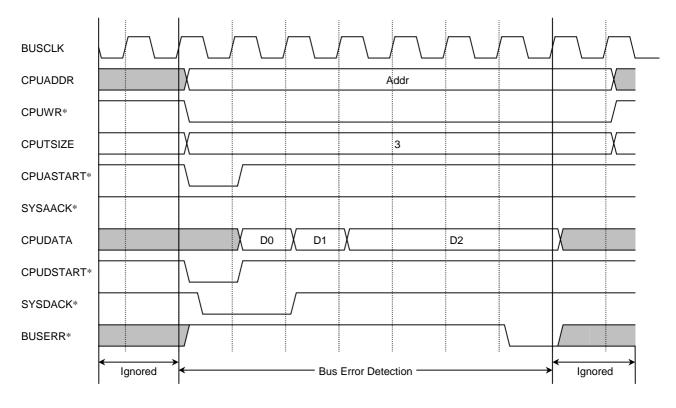

| 8.                                                                                                                                | 5.6 Bu                                                                                                                                                                                            | us Error Operations                                                                                                                                                                                                                                                                   | 8-25                                                                                                                                  |

|                                                                                                                                   | 8.5.6.1                                                                                                                                                                                           | Bus Error Exceptions                                                                                                                                                                                                                                                                  | 8-25                                                                                                                                  |

|                                                                                                                                   | 8.5.6.2                                                                                                                                                                                           | CPU Bus Cycle Termination                                                                                                                                                                                                                                                             | 8-26                                                                                                                                  |

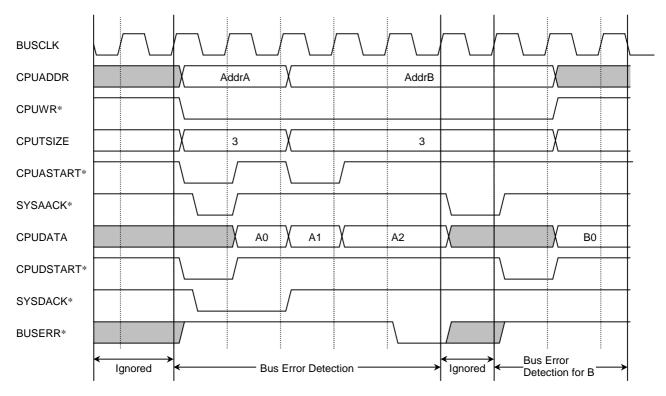

|                                                                                                                                   | 8.5.6.3                                                                                                                                                                                           | Bus Error Timing with No Pending Operation                                                                                                                                                                                                                                            | 8-26                                                                                                                                  |

|                                                                                                                                   | 8.5.6.4                                                                                                                                                                                           | Bus Error Timing with One Pending Operation                                                                                                                                                                                                                                           | 8-26                                                                                                                                  |

|                                                                                                                                   | 8.5.6.5                                                                                                                                                                                           | Bus Error Timing with Two Pending Operations                                                                                                                                                                                                                                          | 8-28                                                                                                                                  |

|                                                                                                                                   | _                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                       | 9-1                                                                                                                                   |

| 9. Pf                                                                                                                             | erformar                                                                                                                                                                                          | ice Counter                                                                                                                                                                                                                                                                           |                                                                                                                                       |

|                                                                                                                                   |                                                                                                                                                                                                   | nce Counter                                                                                                                                                                                                                                                                           |                                                                                                                                       |

| 9.1                                                                                                                               | Overvi                                                                                                                                                                                            | ew                                                                                                                                                                                                                                                                                    | 9-2                                                                                                                                   |

| 9.1<br>9.2                                                                                                                        | Overvi<br>Perforr                                                                                                                                                                                 | ew<br>mance Counters and Performance Control Registers                                                                                                                                                                                                                                | 9-2<br>9-2                                                                                                                            |

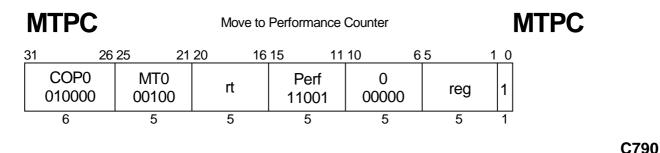

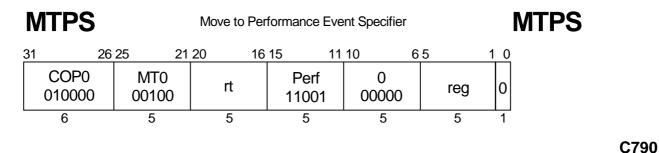

| 9.1<br>9.2<br>9.2                                                                                                                 | Overvi<br>Perforr<br>2.1 Ac                                                                                                                                                                       | ew<br>mance Counters and Performance Control Registers<br>ccessing Counters and Registers                                                                                                                                                                                             | 9-2<br>9-2<br>9-3                                                                                                                     |

| 9.1<br>9.2<br>9.:<br>9.:                                                                                                          | Overvi<br>Perforr<br>2.1 Ac<br>2.2 St                                                                                                                                                             | ew<br>mance Counters and Performance Control Registers<br>ccessing Counters and Registers<br>ate of Performance Counter Control Registers Upon Reset                                                                                                                                  | 9-2<br>9-2<br>9-3<br>9-4                                                                                                              |

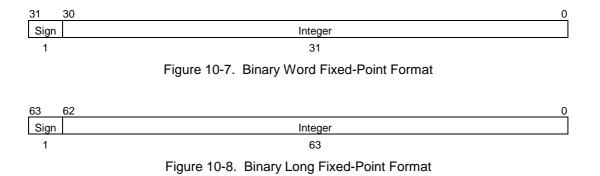

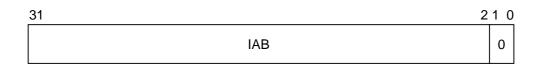

| 9.1<br>9.2<br>9.1<br>9.1                                                                                                          | Overvi<br>Perforr<br>2.1 Ac<br>2.2 St<br>Counte                                                                                                                                                   | ew<br>mance Counters and Performance Control Registers<br>ccessing Counters and Registers<br>ate of Performance Counter Control Registers Upon Reset<br>er Operation                                                                                                                  | 9-2<br>9-2<br>9-3<br>9-4<br>9-5                                                                                                       |